The fetch–decode–execute (FDE) cycle is the heartbeat of the CPU. This guide breaks down each stage, highlights essential registers (PC, MAR, MDR, CIR), and shares tips to maximise marks in OCR GCSE exam questions.

Step-by-Step

- Fetch: PC holds the next instruction address → copied to MAR; instruction fetched from memory into MDR.

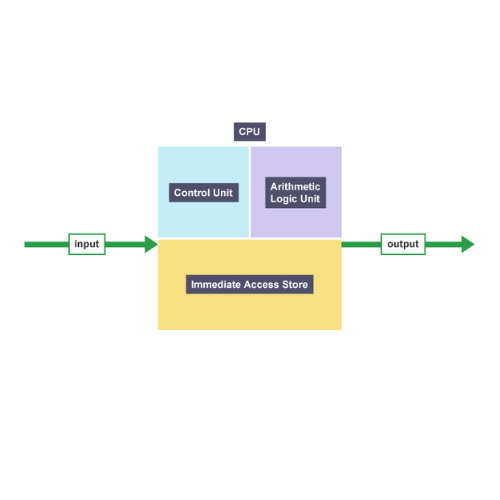

- Decode: Instruction moved into CIR; the Control Unit decodes it.

- Execute: ALU/CPU executes the instruction (e.g., add, load/store). The PC updates to the next instruction.

Registers to learn

- PC (Program Counter): Address of the next instruction.

- MAR (Memory Address Register): Holds the address to access in memory.

- MDR (Memory Data Register): Holds the data/instruction read from memory.

- CIR (Current Instruction Register): Holds the instruction being decoded/executed.

- ACC (Accumulator): Often stores intermediate ALU results (useful context).

Exam tips

- Name the registers and their roles (PC, MAR, MDR, CIR) explicitly.

- Use the language of the spec: fetch → decode → execute.

- Include how the PC changes and mention the Control Unit/ALU where relevant.

Practice prompt (8 marks)

“Explain the fetch–decode–execute cycle, referring to registers and the CPU’s control unit.”

Model answer structure (tap to reveal)

- Overview: The CPU repeatedly performs FDE for each instruction.

- Fetch: PC → MAR; memory → MDR; instruction → CIR.

- Decode: CU decodes the instruction in CIR; identify required operands/registers.

- Execute: ALU/CPU performs operation; PC increments (or jumps if branch).

- Close: Emphasise continuous cycle and correct register names.

Interactive simulator

Bring the cycle to life and step through each stage.

Launch Simulator

Key takeaways

- State each stage clearly: fetch, decode, execute.

- Reference PC, MAR, MDR, CIR (and ACC if relevant) accurately.

- Diagrams + precise register roles = easy marks.